This afternoon, we locked the OMC at dark fringe and performed the hand off of DARM to DC readout.

ITF locked in CARM null at the beginning of the shift.

DARM offset set to -0.2.

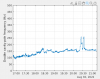

OMC locked on B1_PD3 at 15h12 utc. DARM_SET increased to -0.3. ITF unlocked when trying to perform the hand-off of DARM to DC readout at 15h24 utc. (Fig.1)

ITF relocked in CARM null.

OMC scan started at 15h44m50 utc for optical characterization, ended at 16h05m40 utc (Fig.2)

DARM_SET to -0.5

Trying to lock OMC with OMC_LOCK: attempt failed. The node returned the following error message:

2022-08-30-16h11m07-UTC>WARNING-[ACQUIRE_OMC1.main] USERMSG 0: EZCA CONNECTION ERROR: Could not get value from channel: SDB2_B1_PD3_VBias

We tried to reload the OMC_LOCK node, but it got stuck. We put it in PAUSE.

We then locked the OMC with VPM at 16h23m30 utc (Fig.3)

DARM offset increased to -0.75

Hand-off DARM to DC readout with B1_PD3 at 16h35m50 utc

Check that B1 PD1+PD2 audio is not saturating. Audio below 0.1 mW (saturation should be at 0.4 mW)

Hand-off of DARM to B1 PD1+PD2 at 16h44m20 utc

Tuned B1 PD2 demodulation phase. Config file updated at 17h01m53 UTC

Tuned gain of error signal B1_f1_i_DCn_err. Config file updated at 17h32m48-UTC.

Leaving the ITF locked in DC readout for the rest of the shift (until ~21h utc) to allow ISC noise injections – Fig.3

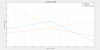

Performed OMC lock hand-off to B1_PD2 at 20h52m07 utc. Go back to B1_PD3 at 21h07m59 utc. Fig.4 shows the spectrum of the OMC error signal before (purple) and after (blue) the hand-off. Note that this hand-off was almost transparent for the ITF lock.

ITF manually unlocked by unlocking the OMC at 21h11m08-UTC.

OMC shutter closed and OMC_LOCK node put in TEMP_CONTROLLED state.