This morning we tried to consolidate the misaligned configuration for the SR mirror in order to get the best sensitivity in the bucket.

We had the possibility to use 2 signals: the double demodulation of DARM in the bucket or simply the DCP. The first error signal is currently not sensitive to SR alignment (to be checked if a computation problem is present) so, we studied the possibilty to implement the second one.

We then misaligned the SR ty, keeping the SR tx engaged with the standard loop and re-engaging the servo on the BS ty set point (gain 1e-6).

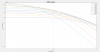

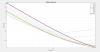

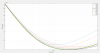

We have reached 50Mpc with a misalignment of SR ty larger than 2urad. See Figure 1 2 and 3, where the effect of the SR alignment is visible (this time the maximum of low frequency OG was not reached even for DCP of about 160Hz).

To be noticed that the SDB powers do not drop (only as small decrease of the 112MHz).

We engaged the new error signal by hand and we unlocked by setting the set point to 150 for a failure of DARM (the pole was too close to the DARM ugf).

We have put in the automation the engagment of the new error signal with a set point of 220Hz of DCP, but we could not test it due to the PSL failure.

---- to come back to the usual alignment control -------------

comment lines 6042-6045 in ITF_LOCK.py