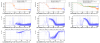

This morning we set up the demodulation of the B1p_PD1_56MHz at 40KHz, see the time sequence .

- the B1p_PD1_56MHz signals built by the demodulation mezzanine are now acquired at 40KHz instead of 10KHz previously

- After the demodulation mezzanine reconfiguration, the phase of the 100MHz Timing clock acquired by the same demodulation board remained at the same value

- At the SDB2_Photodiode server , there is now 2 parts related to the B1p_PD1_56MHz demodulation

- the standard one for the 10KHz processing

- The input channels now acquired at 40KHz are filtered and decimated at 10KHz with a dedicated filter called "flt_40KHzTo10KHz" to have the same delay as previously.

- and the other for the 40KHz one

- the LNFS_56MHz phase available at 10KHz has been extended to 40KHz using its sinus and cosine .

- the B1p_PD1 56MHz demodulation at 40KHz has been setup , with the facilties to perform the demodulation noises mitigation if needed . These mitigations are by default disabled

- The DAQ channels available are:

- the demodulation outputs: SDB2_B1p_PD1_56MHz_{I,Q}_40KHz and SDB2_B1p_PD1_56MHz_{mag,phi}_FS

- the demodulation phases: SDB2_B1p_56MHz_phi0_40KHz, SDB2_B1p_PD1_56MHz_phi0_40KHz

- and the demodulation amplitude and phase noise corrections: SDB2_B1p_PD1_56MHz_6MHz_ampl_noise_corr_40KHz_FS and SDB2_B1p_PD1_56MHz_phase_noise_corr_40KHz_FS

- the standard one for the 10KHz processing